気が付いたら3年もあけてしまった。

何年か前、ヤフオクを眺めていたところEasy Z80の基板が出品されていたので、さっそく落札した。

しばらくの間、10MHzで動くZ80SIO,CTCが手に入らず何か月か経ってから組み立てを行った。

このボードはRC2014というバスで機能を拡張できるようだったので、CFやIDEやRTCなど少しづつ購入していろいろ付け加えていった。

海外のサイトからの購入なので、すこし不安があったが無事に届いて安心した。

さて、話はかわって、秋月電子のAKI-80はいつのまにか終売となって、Super AKI-80も在庫限りで秋葉原店で投げ売りされていた。

手持ちのAKI-80やSuper AKI-80を眺めながら何か作れないかなを思い、ネットを眺めているとCP/Mを動かしたりしているのをいくつか見つけた。

そしてふとRomWBWを動かせないかと思いついたので、さらにネットを調べてみたがX(Twitter)で動いたという報告が1件あるだけだった。

どうしたものか調べてみると、RomWBWはTiny Z80に対応していて、そのTiny Z80はザイログのZ84C15が使用されている。

Z84C15は東芝のTMPZ84C015を元に作られていて、一部のピンとIO上にある設定用レジスタに違いはあるものの、ほぼ互換となっている。

ならば自分でもAKI-80でRomWBWを動かしてみようと思い、さっそく作ってみた。

クロック周りはTiny Z80を参考にしている。

まずはAKI-80で動くかどうか確認をかねて組み立て。

RomWBWもAKI-80用にコンフィグファイルを準備してアセンブルする。

コンフィグファイルはTiny Z80用のものを参考にした。

最初はうまく起動しなくて、ハード的・ソフト的にいろいろ調べてみた。

ハード的にはリセットにノイズが乗っていたようで、最終的にはAKI-80上のリセット周りは取り外した。

ソフト的には「hbios.asm」の一部に誤りらしきものがあったので、そこも修正。

v3.5.1を元に修正ファイルは \RomWBW-release\RomWBW-v3.5.1-Package\Source\HBIOS にある「hbios.asm」の1728行目以降。

修正箇所は以下の通り。

修正前

#IF (EIPCENABLE) LD A,(EIPC_WDT_CONST | EIPC_HALT_RUN | EIPC_WDT_P2_22) OUT (EIPC_WDTMR),A ; CLEAR WDTE BIT (DISABLE WATCHDOG) LD A,EIPC_DIS_WDT ; DISABLE WDT - SECOND KEY OUT (EIPC_WDTCR),A LD A,EIPC_WCR ; SET SYSTEM CONTROL REGISTER POINTER ; (SCRP) TO POINT TO WAIT STATE OUT (EIPC_SCRP),A ; CONTROL REGISTER (WCR) LD A,(EIPC_IO_0WS | EIPC_MEM_OWS | EIPC_OCF_0WS | EIPC_INT_0WS | EIPC_CHAIN_0WS) OUT (EIPC_SCDP),A ; NO WAIT STATES LD A,EIPC_MCR ; SET SCRP TO POINT TO MISCELLANEOUS OUT (EIPC_SCRP),A ; CONTROL REGISTER (MCR) LD A,EIPC_CLKDIV1 ; DIVIDE CLOCK BY 1, /CS0 DISABLE OUT (EIPC_SCDP),A ; SET SYSTEM CONTROL DATA PORT (SCDP) #ENDIF

修正後

#IF (EIPCENABLE) LD A,EIPC_WDT_CONST | EIPC_HALT_RUN | EIPC_WDT_P2_22 OUT (EIPC_WDTMR),A ; CLEAR WDTE BIT (DISABLE WATCHDOG) LD A,EIPC_DIS_WDT ; DISABLE WDT - SECOND KEY OUT (EIPC_WDTCR),A ; LD A,EIPC_WCR ; SET SYSTEM CONTROL REGISTER POINTER ; (SCRP) TO POINT TO WAIT STATE ; OUT (EIPC_SCRP),A ; CONTROL REGISTER (WCR) ; LD A,EIPC_IO_0WS | EIPC_MEM_OWS | EIPC_OCF_0WS | EIPC_INT_0WS | EIPC_CHAIN_0WS ; OUT (EIPC_SCDP),A ; NO WAIT STATES ; LD A,EIPC_MCR ; SET SCRP TO POINT TO MISCELLANEOUS ; OUT (EIPC_SCRP),A ; CONTROL REGISTER (MCR) ; LD A,EIPC_CLKDIV1 ; DIVIDE CLOCK BY 1, /CS0 DISABLE ; OUT (EIPC_SCDP),A ; SET SYSTEM CONTROL DATA PORT (SCDP) #ENDIF

LD A,(~)のところをLD A,~に修正。

かっこの有無で意味が変わってくるが、説明は省略。

あとは、Z84C15で追加されてTMPZ84C015には無いレジスタの設定はコメントアウト。

ここはコメントアウトしなくても、I/Oを空振りするだけなので直さなくてもよいかも。

いろいろ修正して動くようになったが、今度はCFモジュールをつけるとCTCが見えなくなる。

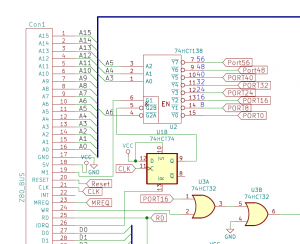

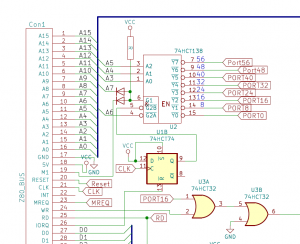

なぜだろうと回路図を眺めると、CFモジュールのアドレスデコードでA7を見ていないことが分かった。

この状態だと、I/Oアドレスの0x10と0x90の両方に反応して、CTCのアドレスとかち合ってしまっている。

これに対応するためCFモジュールの修正を行った。

具体的には、アドレスバスのA7をM1とANDを取るようにダイオードとプルアップ抵抗を追加。

これでI/Oアドレスの0x90でのみ反応するようになった。

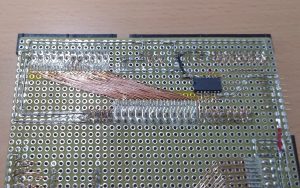

基板については、M1から74HCT138へ伸びているパターンをカットして、基板裏面にダイオードと抵抗を追加した。

とりあえずAKI-80で動くことを確認したら、今度は」Super AKI-80のほうに取り掛かった。

こちらは82C265(82C55 × 2)が付いていて、せっかくだからIDEの機能を乗せることにした。

IDEについては、RFC2014のサイトにあるIDE Hard Drive Moduleにある回路図を参考に配線する。

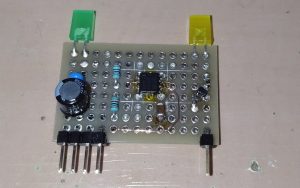

電源投入時にコンソールから起動メッセージが表示されても、こちらからの文字が入力できず、リセットしてから再起動後に入力できるようになることがあるので、リセットICのM51957Bを使って電源投入時の約1秒間リセット信号を送るようにモジュールを組む。

これで、電源投入して起動したあとのコンソール入力も問題なくできるようになった。

AKI-80とSuper AKI-80にメモリーなどいろいろ載せて動かしているところ。

Super AKI-80はIDEでコンパクトフラッシュをつないでいるので縦長になってしまった。

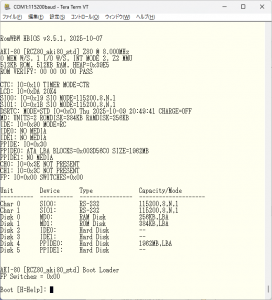

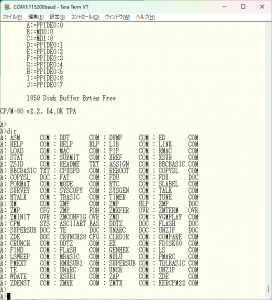

TeraTermの表示内容。

PPIDEがSuper AKI-80上のPPI(82C265)の0番を指していている。

RomWBWのコンフィグファイルもSuper AKI-80に合わせて直してある。

最後にコンフィグファイルの内容。

\RomWBW-v3.5.1-Package\Source\HBIOS\Config 内に「RCZ80_aki80_std.asm」というファイルを作成して、あとは\RomWBW-v3.5.1-Package\Source\HBIOS にある Buildコマンドでアセンブルするだけ。

; ;================================================================================================== ; ROMWBW DEFAULT BUILD SETTINGS FOR TINY Z80 ;================================================================================================== ; ; THIS FILE DEFINES THE DEFAULT CONFIGURATION SETTINGS FOR THE PLATFORM ; INDICATED ABOVE. THESE SETTINGS DEFINE THE OFFICIAL BUILD FOR THIS ; PLATFORM AS DISTRIBUTED IN ROMWBW RELEASES. ; ; ROMWBW USES CASCADING CONFIGURATION FILES AS INDICATED BELOW: ; ; cfg_MASTER.asm - MASTER: CONFIGURATION FILE DEFINES ALL POSSIBLE ROMWBW SETTINGS ; | ; +-> cfg_<platform>.asm - PLATFORM: DEFAULT SETTINGS FOR SPECIFIC PLATFORM ; | ; +-> Config/<plt>_std.asm - BUILD: SETTINGS FOR EACH OFFICIAL DIST BUILD ; | ; +-> Config/<plt>_<cust>.asm - USER: CUSTOM USER BUILD SETTINGS ; ; THE TOP (MASTER CONFIGURATION) FILE DEFINES ALL POSSIBLE ROMWBW ; CONFIGURATION SETTINGS. EACH FILE BELOW THE MASTER CONFIGURATION FILE ; INHERITS THE CUMULATIVE SETTINGS OF THE FILES ABOVE IT AND MAY ; OVERRIDE THESE SETTINGS AS DESIRED. ; ; OTHER THAN THE TOP MASTER FILE, EACH FILE MUST "#INCLUDE" ITS PARENT ; FILE (SEE #INCLUDE STATEMENT BELOW). THE TOP TWO FILES SHOULD NOT BE ; MODIFIED. ; ; TO CUSTOMIZE YOUR BUILD SETTINGS YOU SHOULD MODIFY THIS FILE, THE ; DEFAULT BUILD SETTINGS (Config/<platform>_std.asm) OR PREFERABLY ; CREATE AN OPTIONAL CUSTOM USER SETTINGS FILE THAT INCLUDES THE DEFAULT ; BUILD SETTINGS FILE (SEE EXAMPLE Config/SBC_user.asm). ; ; BY CREATING A CUSTOM USER SETTINGS FILE, YOU ARE LESS LIKELY TO BE ; IMPACTED BY FUTURE CHANGES BECAUSE YOU WILL BE INHERITING MOST ; OF YOUR SETTINGS WHICH WILL BE UPDATED BY AUTHORS AS ROMWBW EVOLVES. ; ; PLEASE REFER TO THE CUSTOM BUILD INSTRUCTIONS (README.TXT) IN THE ; SOURCE DIRECTORY (TWO DIRECTORIES ABOVE THIS ONE). ; ; *** WARNING: ASIDE FROM THE MASTER CONFIGURATION FILE, YOU MUST USE ; ".SET" TO OVERRIDE SETTINGS. THE ASSEMBLER WILL ERROR IF YOU ATTEMPT ; TO USE ".EQU" BECAUSE IT WON'T LET YOU REDEFINE A SETTING WITH ".EQU". ; #DEFINE PLATFORM_NAME "AKI-80", " [", CONFIG, "]" #DEFINE AUTO_CMD "" ; AUTO CMD WHEN BOOT_TIMEOUT IS ENABLED #DEFINE DEFSERCFG SER_115200_8N1 | SER_RTS ; DEFAULT SERIAL CONFIGURATION ; #INCLUDE "cfg_RCZ80.asm" ; BOOT_TIMEOUT .SET -1 ; AUTO BOOT TIMEOUT IN SECONDS, -1 TO DISABLE, 0 FOR IMMEDIATE BOOT_PRETTY .SET FALSE ; BOOT WITH PRETTY PLATFORM NAME AUTOCON .SET TRUE ; ENABLE CONSOLE TAKEOVER AT LOADER PROMPT ; CPUOSC .SET 8000000 ; CPU OSC FREQ IN MHZ INTMODE .SET 2 ; INTERRUPTS: 0=NONE, 1=MODE 1, 2=MODE 2, 3=MODE 3 (Z280) ; CTCENABLE .SET TRUE ; ENABLE ZILOG CTC SUPPORT CTCBASE .SET $10 ; CTC BASE I/O ADDRESS CTCTIMER .SET TRUE ; ENABLE CTC PERIODIC TIMER CTCMODE .SET CTCMODE_CTR ; CTC MODE: CTCMODE_[NONE|CTR|TIM16|TIM256] CTCOSC .SET 921600 ; CTC CLOCK FREQUENCY EIPCENABLE .SET TRUE ; EIPC: ENABLE Z80 EIPC (Z84C15) INITIALIZATION WDOGMODE .SET WDOG_NONE ; WATCHDOG MODE: WDOG_[NONE|EZZ80|SKZ] WDOGIO .SET $6F ; WATCHDOG REGISTER ADR ; FPLED_ENABLE .SET TRUE ; FP: ENABLES FRONT PANEL LEDS FPSW_ENABLE .SET TRUE ; FP: ENABLES FRONT PANEL SWITCHES LCDENABLE .SET TRUE ; ENABLE LCD DISPLAY CRTACT .SET FALSE ; ACTIVATE CRT (VDU,CVDU,PROPIO,ETC) AT STARTUP VDAEMU_SERKBD .SET $FF ; VDA EMULATION: SERIAL KBD UNIT #, OR $FF FOR HW KBD ; DSRTCENABLE .SET TRUE ; DSRTC: ENABLE DS-1302 CLOCK DRIVER (DSRTC.ASM) RP5RTCENABLE .SET FALSE ; RP5C01 RTC BASED CLOCK (RP5RTC.ASM) INTRTCENABLE .SET TRUE ; ENABLE PERIODIC INTERRUPT CLOCK DRIVER (INTRTC.ASM) ; DUARTENABLE .SET FALSE ; DUART: ENABLE 2681/2692 SERIAL DRIVER (DUART.ASM) UARTENABLE .SET FALSE ; UART: ENABLE 8250/16550-LIKE SERIAL DRIVER (UART.ASM) ACIAENABLE .SET FALSE ; ACIA: ENABLE MOTOROLA 6850 ACIA DRIVER (ACIA.ASM) SIOENABLE .SET TRUE ; SIO: ENABLE ZILOG SIO SERIAL DRIVER (SIO.ASM) SIO0MODE .SET SIOMODE_STD ; SIO 0: CHIP TYPE: SIOMODE_[STD|RC|SMB|ZP|Z80R] SIO0BASE .SET $18 ; SIO 0: REGISTERS BASE ADR SIO0ACLK .SET 1843200 ; SIO 0A: OSC FREQ IN HZ, ZP=2457600/4915200, RC/SMB=7372800 SIO0BCLK .SET 1843200 ; SIO 0B: OSC FREQ IN HZ, ZP=2457600/4915200, RC/SMB=7372800 SIO1ACLK .SET 7372800 ; SIO 1A: OSC FREQ IN HZ, ZP=2457600/4915200, RC/SMB=7372800 SIO1BCLK .SET 7372800 ; SIO 1B: OSC FREQ IN HZ, ZP=2457600/4915200, RC/SMB=7372800 ; TMSENABLE .SET FALSE ; TMS: ENABLE TMS9918 VIDEO/KBD DRIVER (TMS.ASM) TMSMODE .SET TMSMODE_MSX ; TMS: DRIVER MODE: TMSMODE_[SCG|N8|MSX|MSXKBD|MSXMKY|MBC|COLECO|DUO|NABU] TMS80COLS .SET FALSE ; TMS: ENABLE 80 COLUMN SCREEN, REQUIRES V9958 TMSTIMENABLE .SET FALSE ; TMS: ENABLE TIMER INTERRUPTS (REQUIRES IM1) VRCENABLE .SET FALSE ; VRC: ENABLE VGARC VIDEO/KBD DRIVER (VRC.ASM) EFENABLE .SET FALSE ; EF: ENABLE EF9345 VIDEO DRIVER (EF.ASM) ; FDENABLE .SET FALSE ; FD: ENABLE FLOPPY DISK DRIVER (FD.ASM) FDMODE .SET FDMODE_RCWDC ; FD: DRIVER MODE: FDMODE_[DIO|ZETA|ZETA2|DIDE|N8|DIO3|RCSMC|RCWDC|DYNO|EPFDC|MBC] FD0TYPE .SET FDT_3HD ; FD 0: DRIVE TYPE: FDT_[3DD|3HD|5DD|5HD|8] FD1TYPE .SET FDT_3HD ; FD 1: DRIVE TYPE: FDT_[3DD|3HD|5DD|5HD|8] ; IDEENABLE .SET TRUE ; IDE: ENABLE IDE DISK DRIVER (IDE.ASM) IDE0BASE .SET $90 ; IDE 0: IO BASE ADDRESS ; PPIDEENABLE .SET TRUE ; PPIDE: ENABLE PARALLEL PORT IDE DISK DRIVER (PPIDE.ASM) PPIDE0BASE .SET $30 ; PPIDE 0: PPI REGISTERS BASE ADR ; SDENABLE .SET FALSE ; SD: ENABLE SD CARD DISK DRIVER (SD.ASM) SDMODE .SET SDMODE_PIO ; SD: DRIVER MODE: SDMODE_[JUHA|N8|CSIO|PPI|UART|DSD|MK4|SC|MT|USR|PIO|Z80R|EPITX|FZ80|GM|EZ512|K80W] SDCNT .SET 1 ; SD: NUMBER OF SD CARD DEVICES (1-2), FOR DSD/SC/MT ONLY ; CHENABLE .SET TRUE ; CH: ENABLE CH375/376 USB SUPPORT ; PRPENABLE .SET FALSE ; PRP: ENABLE ECB PROPELLER IO BOARD DRIVER (PRP.ASM) ; LPTENABLE .SET FALSE ; LPT: ENABLE CENTRONICS PRINTER DRIVER (LPT.ASM) ; PPAENABLE .SET FALSE ; PPA: ENABLE IOMEGA ZIP DRIVE (PPA) DISK DRIVER (PPA.ASM) IMMENABLE .SET FALSE ; IMM: ENABLE IOMEGA ZIP PLUS DRIVE (IMM) DISK DRIVER (IMM.ASM) SYQENABLE .SET FALSE ; SYQ: ENABLE SYQUEST SPARQ DISK DRIVER (SYQ.ASM) ; SN76489ENABLE .SET FALSE ; SN: ENABLE SN76489 SOUND DRIVER ; AY38910ENABLE .SET FALSE ; AY: ENABLE AY-3-8910 / YM2149 SOUND DRIVER AY_CLK .SET 1789772 ; AY: PSG CLOCK FREQ, ASSUME MSX STD AYMODE .SET AYMODE_RCZ80 ; AY: DRIVER MODE: AYMODE_[SCG|N8|RCZ80|RCZ180|MSX|LINC|MBC|DUO|NABU] AY_FORCE .SET FALSE ; AY: BYPASS AUTO-DETECT, FORCED PRESENT